Project Goals

The overall project goal of the COSRECOS project is to simplify the design and operation of partially reconfigurable systems such that this technology can be used for real world applications. In particular we investigate the following topics in our project:

- Tools for on-FPGA communication synthesis and floorplan

ning - Methodologies for preemptive execution of hardware modules running on an FPGA

- Techniques for high-speed reconfiguration

- Modeling of run-time reconfigurable systems

- Theoretical analysis of run-time reconfigurable systems (latencies, buffer/memory requirements or configuration overhead)

- Simulation

- Automated component-based design for static and partially reconfigurable systems

- Demonstrator implementations (preferably from the networking/communication system domain)

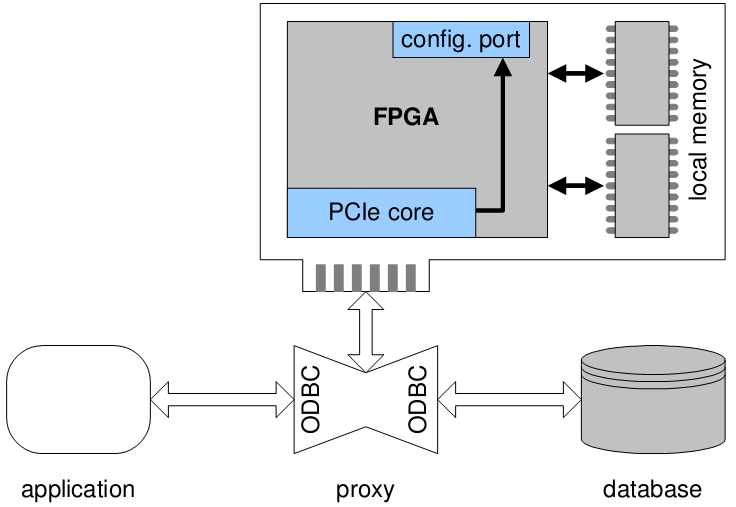

Current Project: Database Acceleration:

We integrate an FPGA database accelerator by adding a proxy between the application and the database. The accelerator hardware provides 24GB of local memory in order to cache tables from the original software database. Considering an SQL read query from the application to the database, the proxy can forward the request to the FPGA accelerator whenever suitable. Otherwise the proxy is forwarding the query to the original software database (MySQL). On the FPGA, a dataflow machine is created on-the-fly by stitching together preimplemented hardware modules (i.e. SQL accelerator modules). We are currently testing our dynamic dataflow machine with a 512 bit datapath running at 300 MHz. The implementation is based on a MAX3 system from Maxeler providing us with fast PCIe and fast DDR3 memory access out of the box.